Die bitorientierten Realisierungsvarianten sind insbesondere bei Hardware-Implementierungen sehr

effizient, können aber auch softwaretechnisch emuliert werden. Die Verarbeitung erfolgt dabei mittels

rückgekoppelter Schieberegister (Linear Feedback Shift Register, LFSR), dessen Inhalt nach der

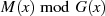

letzten Verschiebung den (modulo-2) Divisionsrest darstellt [4]. In Abbildung 1 ist das

Grundprinzip eines solchen Divisions-Schieberegisters, welches  berechnet,

dargestellt.8

berechnet,

dargestellt.8

Die Stellung der XOR-Gatter (Symbol  ) wird durch die Koeffizienten

) wird durch die Koeffizienten  von

von  , für die

, für die

gilt, bestimmt.

gilt, bestimmt.

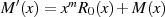

Nachteil dieser Variante ist, daß die Multiplikation  , also das Nachstellen von

, also das Nachstellen von  Null-Bits vor

der Verarbeitung im LFSR notwendig ist. Eine Alternative dazu zeigt Abbildung 2, in der diese

Operation durch Einspeisen von

Null-Bits vor

der Verarbeitung im LFSR notwendig ist. Eine Alternative dazu zeigt Abbildung 2, in der diese

Operation durch Einspeisen von  an der Stelle

an der Stelle  durch das Schieberegister selbst vorgenommen

wird.

durch das Schieberegister selbst vorgenommen

wird.

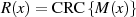

An dieser Stelle soll noch geklärt werden, welchen Einfluß ein bestimmter Start- bzw. Anfangsrest, auf den das

LFSR in Abbildung 1 voreingestellt wird, auf den ursprünglich nach Gleichung 1 berechneten CRC-Wert

hat.9

Dazu kann der Anfangswert  als der Nachricht

als der Nachricht  vorangestellt aufgefaßt werden.

vorangestellt aufgefaßt werden.

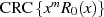

Bildet man nun den CRC-Rest für die Gesamtnachricht  , also

, also

![CRC {M ′(x)} = xk [xmR (x)+ M (x)] mod G(x)

k m 0 k

= xx R0 (x) mod G(x)+ x M (x) mod G (x)

= CRC {xmR0(x)}+ CRC {M (x)},](crc122x.png)

dann ist sofort erkennbar, daß der ohne Anfangsrest entstehende Rest

durch Modulo-2-Addition mit

durch Modulo-2-Addition mit  modifiziert

wird.10

modifiziert

wird.10

In der Praxis ist das Verfahren außerdem noch in bestimmten Modifikationen anzutreffen, z. B. Anhängen des invertierten CRC-Restes beim HDLC-Protokoll.